Dalam catatan ini kami membincangkan secara komprehensif 3 litar sensor jarak dekat dengan banyak litar aplikasi dan ciri terperinci litar. Litar sensor jarak dekat kapasitif pertama menggunakan konsep berasaskan IC 741 dan IC 555 yang sederhana, sementara yang terakhir sedikit lebih tepat dan menggabungkan reka bentuk berasaskan ketepatan IC PCF8883

1) Menggunakan IC 741

Litar yang dijelaskan di bawah ini dapat dikonfigurasi untuk mengaktifkan geganti atau beban yang sesuai seperti a paip air , sebaik sahaja tubuh manusia atau tangan menghampiri plat sensor kapasitif. Dengan keadaan tertentu jarak tangan hanya cukup untuk mencetuskan output litar.

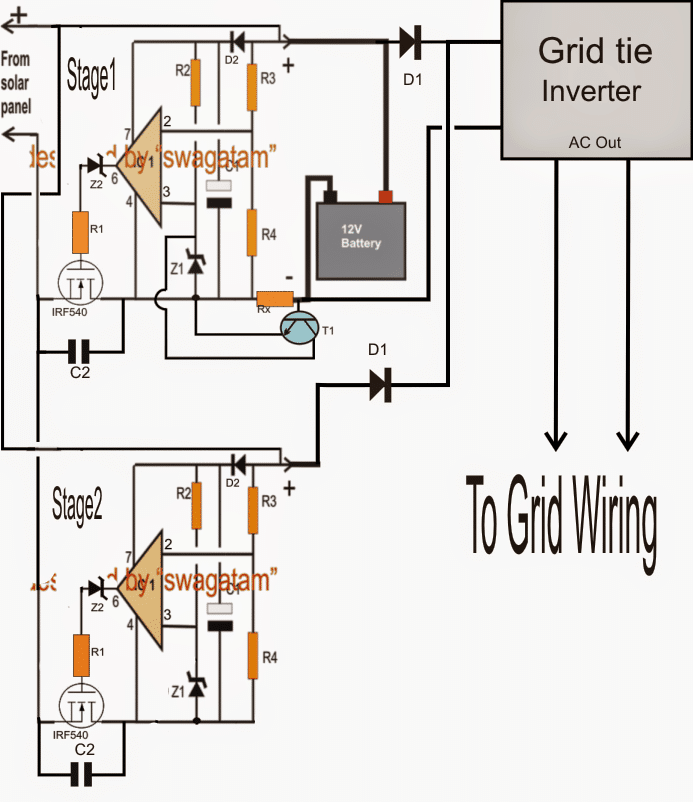

Input impedans tinggi diberikan oleh Q1, yang merupakan transistor kesan medan biasa seperti 2N3819. Penguat op 741 standard digunakan dalam bentuk suis tahap voltan sensitif yang kemudiannya menggerakkan penyangga arus Q2, transistor bnolar pnp arus sederhana, sehingga mengaktifkan relay yang mungkin terbiasa menukar peranti, seperti penggera, keran dll. .

Semasa litar berada dalam keadaan sedia siaga, voltan pada pin 3 op amp dipasang pada tahap lebih besar daripada tahap voltan pin 2 dengan menyesuaikan VR1 yang telah ditetapkan.

Ini memastikan bahawa voltan pada pin output 6 akan tinggi menyebabkan transistor Q2 dan relay tetap dimatikan.

Apabila jari dibawa berdekatan dengan plat sensor atau menyentuh dengan ringan, penurunan VGS bias yang berlawanan akan meningkatkan arus pengaliran FET Q1 dan penurunan voltan R1 yang dihasilkan akan mengurangkan voltan pin op amp 3 di bawah voltan yang ada pada pin 2.

Ini akan menyebabkan voltan pin 6 jatuh dan seterusnya menghidupkan relay dengan menggunakan Q2. Resistor R4 mungkin ditentukan agar relay terus dimatikan dalam keadaan normal, mengingat voltan set positif yang kecil mungkin berkembang pada output op amp pin 6 walaupun voltan pin 3 kebetulan lebih rendah daripada voltan pin 2 di keadaan senyap (terbiar). Masalah ini dapat diatasi hanya dengan menambahkan LED secara bersiri dengan pangkalan Q2.

2) Menggunakan IC 555

Catatan tersebut menerangkan litar sensor jarak dekat kapasitif IC 555 yang berkesan yang boleh digunakan untuk mengesan penceroboh berhampiran objek berharga seperti kenderaan anda. Idea itu diminta oleh Encik Max Payne.

Permintaan Litar

Helo Swagatam,

Sila Lampirkan Litar Kapasitif / Badan / Sensitif yang boleh digunakan pada basikal. Peranti seperti itu dilihat pada sistem keselamatan kereta, Apabila seseorang mendekati kereta atau jarak 1 in yang sederhana akan mencetuskan penggera selama 5 saat.

Bagaimana penggera jenis ini berfungsi, penggera hanya akan memicu apabila seseorang mendekat (katakan 30cm) jenis sensor apa yang mereka gunakan?

Rajah Litar

Gambar Litar Kesopanan: Elektor Elektronik

Rekaan

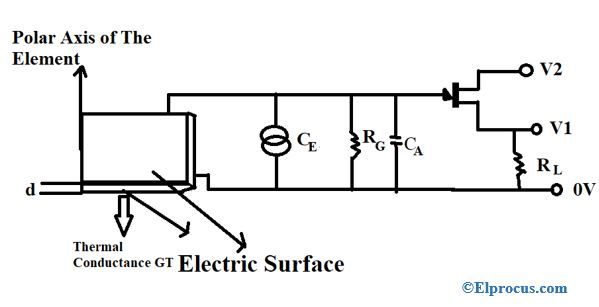

Litar sensor kapasitif dapat difahami dengan bantuan penerangan berikut:

IC1 pada dasarnya berwayar sebagai astable, tetapi tanpa memasukkan kapasitor sebenar. Di sini plat kapasitif diperkenalkan dan mengambil kedudukan kapasitor yang diperlukan untuk operasi astabel.

Perlu diketahui bahawa plat kapasitif yang lebih besar akan menghasilkan tindak balas yang lebih baik dan boleh dipercayai dari litar.

Oleh kerana litar ini dimaksudkan untuk berfungsi sebagai sistem keselamatan peringatan jarak kendaraan, badan itu sendiri dapat digunakan sebagai pelat kapasitif, dan jumlahnya sangat besar sesuai dengan aplikasinya.

Setelah plat sensor jarak kapasitif disatukan, IC555 berada pada kedudukan siap sedia untuk tindakan yang tidak dapat dilihat.

Ketika mengesan elemen 'ground' pada jarak yang dekat, yang mungkin merupakan tangan manusia, kapasitansi yang diperlukan dikembangkan di seluruh pin2 / 6 dan ground IC.

Perkara di atas menghasilkan peningkatan frekuensi seketika ketika IC mula berayun dalam mod astabnya.

Isyarat astabel diperoleh pada pin3 IC yang disatukan dengan tepat dengan bantuan R3, R4, R5 bersama dengan C3 ---- C5.

Hasil 'bersepadu' dimasukkan ke pentas opamp yang dicoret sebagai pembanding.

Pembanding yang terbentuk di sekitar IC2 bertindak balas terhadap perubahan ini dari IC1 dan menerjemahkannya menjadi voltan pencetus, operasi T1 dan geganti yang sesuai.

Relay boleh dikabelkan dengan siren atau tanduk untuk membimbangkan yang diperlukan.

Walau bagaimanapun, secara praktikalnya dapat dilihat bahawa IC1 menghasilkan denyut voltan positif hingga negatif pada masa yang sama apabila tanah kapasitif dikesan berhampiran plat.

IC2 hanya bertindak balas terhadap kenaikan voltan puncak secara tiba-tiba ini untuk pencetus yang diperlukan.

Sekiranya badan kapasitif terus berada di dekat plat, voltan frekuensi puncak pada pin3 hilang ke tahap yang mungkin tidak dapat dikesan oleh IC2, menjadikannya tidak aktif, yang bermaksud relay tetap aktif hanya pada saat elemen kapasitif dibawa atau dikeluarkan berhampiran permukaan plat.

P1, P2 dapat disesuaikan untuk memperoleh kepekaan maksimum dari plat kapasitif

Untuk mendapatkan tindakan penguncian, output IC2 dapat disatukan lebih jauh ke litar flip flop, menjadikan litar sensor jarak kapasitif sangat tepat dan responsif

3) Menggunakan IC PCF8883

IC PCF8883 dirancang untuk berfungsi seperti suis sensor jarak kapasitif ketepatan melalui teknologi digital yang unik (dipatenkan EDISEN) untuk merasakan perbezaan minimum dalam kapasitansi di sekitar plat penderiaan yang ditentukan.

Ciri-ciri utama

Ciri utama sensor jarak kapasitif khusus ini boleh menjadi kajian seperti yang diberikan di bawah:

Gambar berikut menunjukkan konfigurasi dalaman IC PCF8883

IC tidak bergantung pada tradisional mod penderiaan kapasitansi dinamik sebaliknya mengesan variasi kapasitansi statik dengan menggunakan pembetulan automatik melalui penentukuran automatik berterusan.

Sensor pada dasarnya berbentuk foil konduktif kecil yang dapat disatukan secara langsung dengan pin IC yang relevan untuk penginderaan kapasitif yang dimaksudkan atau mungkin ditamatkan pada jarak yang lebih jauh melalui kabel sepaksi untuk membolehkan operasi penginderaan jarak jauh kapasitif yang tepat dan berkesan

Angka berikut menunjukkan butiran pin IC PCF8883. Fungsi terperinci dari pelbagai pinout dan litar terbina dalam dapat difahami dengan perkara berikut:

Pinout Butiran IC PCF8883

Pinout IN yang seharusnya dihubungkan dengan foil penginderaan kapasitif luaran dihubungkan dengan rangkaian RC dalaman IC.

Masa pelepasan yang diberikan oleh 'tdch' rangkaian RC dibandingkan dengan masa pelepasan rangkaian RC in-bult kedua yang dilambangkan sebagai 'tdchimo'.

Kedua-dua rangkaian RC melalui pengisian berkala oleh VDD (INTREGD) melalui beberapa rangkaian suis yang sama dan disegerakkan, dan kemudian dilepaskan dengan bantuan perintang ke Vss atau tanah

Kadar pelepasan caj ini diatur oleh tingkat persampelan yang dilambangkan dengan 'fs'.

Sekiranya perbezaan potensi dilihat turun di bawah voltan rujukan VM yang ditetapkan secara dalaman, output pembanding yang sesuai cenderung menjadi rendah. Tahap logik yang mengikuti pembanding mengenal pasti pembanding tepat yang sebenarnya boleh bertukar sebelum yang lain.

Dan jika pembanding atas diidentifikasi telah menembak terlebih dahulu, ini menghasilkan pulsa yang diberikan pada CUP, sedangkan jika pembanding yang lebih rendah dikesan telah beralih sebelum ke atas, maka nadi diaktifkan di CDN.

Denyutan di atas terlibat dalam mengawal tahap cas ke atas kapasitor luaran Ccpc yang berkaitan dengan CPC pin. Apabila nadi dihasilkan pada CUP, Ccpc dikenakan melalui VDDUNTREGD untuk jangka waktu tertentu yang memicu peningkatan potensi pada Ccpc.

Cukup pada garis yang sama, ketika nadi diberikan pada CDN, Ccpc dihubungkan dengan peranti sink arus ke tanah yang melepaskan kapasitor menyebabkan potensinya runtuh.

Setiap kali kapasitansi pada pin IN semakin tinggi, ia juga akan meningkatkan masa pelepasan tdch, yang menyebabkan voltan merentasi pembanding yang berkenaan jatuh pada waktu yang lebih lama. Apabila ini berlaku, output pembanding cenderung rendah yang seterusnya menjadikan denyut nadi pada CDN memaksa kapasitor luaran CCP untuk melepaskan ke tahap yang lebih kecil.

Ini menyiratkan bahawa CUP sekarang menghasilkan sebahagian besar denyutan yang menyebabkan CCP dapat diisi lebih banyak lagi tanpa melalui langkah selanjutnya.

Walaupun begitu, ciri penentukuran voltan automatik IC yang bergantung pada peraturan arus tenggelam 'ism' yang dikaitkan dengan pin IN berusaha untuk mengimbangkan masa pelepasan tdch dengan merujuknya dengan tdcmef waktu pelepasan yang ditetapkan secara dalaman.

Voltan merentasi Ccpg dikawal semasa dan menjadi bertanggungjawab untuk pelepasan kapasitansi pada IN dengan cepat apabila potensi merentasi PKC dikesan meningkat. Ini dengan sempurna mengimbangi peningkatan kapasitansi pada pin input IN.

Kesan ini menimbulkan sistem pengesanan gelung tertutup yang secara berterusan memantau dan terlibat secara automatik menyamakan waktu pelepasan tdch dengan merujuk kepada tdchlmf.

Ini membantu membetulkan variasi kapasitans yang perlahan di pin IN IC. Semasa sate pengisian cepat, misalnya ketika jari manusia didekati foil penginderaan dengan cepat, pampasan yang dibincangkan mungkin tidak berlaku, dalam keadaan keseimbangan lamanya tempoh pelepasan tidak berbeza menyebabkan nadi berubah-ubah bergantian melintasi CUP dan CDN.

Ini seterusnya menunjukkan bahawa dengan nilai Ccpg yang lebih besar, variasi voltan yang agak terhad untuk setiap nadi diharapkan untuk CUP atau CDN.

Oleh kerana itu sink arus dalaman menimbulkan pampasan yang lebih perlahan, sehingga meningkatkan kepekaan sensor. Sebaliknya, apabila CCP mengalami penurunan, menyebabkan sensitiviti sensor turun.

Monitor Sensor Dalam Buatan

Tahap kaunter yang terpasang memantau pemicu sensor dan juga menghitung denyutan di CUP atau CDN, penghitung akan diset semula setiap kali arah nadi melintasi CUP ke CDN bergantian atau berubah.

Pin output yang dilambangkan sebagai OUT mengalami pengaktifan hanya apabila jumlah denyutan yang mencukupi di CUP atau CDN dikesan. Tahap gangguan sederhana atau interaksi perlahan merentasi sensor atau kapasitansi input tidak menghasilkan apa-apa kesan pada pemicu output.

Cip ini memperhatikan beberapa keadaan seperti corak pengecasan / pelepasan yang tidak sama sehingga pertukaran output yang disahkan diberikan dan pengesanan palsu dihapuskan.

Permulaan Lanjutan

IC merangkumi litar permulaan yang maju yang membolehkan cip mencapai keseimbangan agak cepat sebaik sahaja bekalan padanya dihidupkan.

Secara dalaman pin OUT dikonfigurasikan sebagai longkang terbuka yang memulai pinout dengan logik tinggi (Vdd) dengan arus maksimum 20mA untuk beban yang dilampirkan. Sekiranya output dikenakan dengan beban lebih dari 30mA, bekalan akan terputus serta-merta kerana fitur perlindungan litar pintas yang langsung terpicu.

Pinout ini juga sesuai dengan CMOS dan oleh itu menjadi sesuai untuk semua peringkat berdasarkan beban CMOS atau litar.

Seperti yang disebutkan sebelumnya, parameter laju pengambilan sampel 'fs' mengaitkan dirinya sebagai 50% dari frekuensi yang digunakan dengan jaringan waktu RC. Kadar pensampelan dapat ditetapkan pada rentang yang telah ditentukan dengan menetapkan nilai CCLIN dengan tepat.

Frekuensi pengayun termodulasi dalaman pada kadar 4% melalui isyarat pseudo-rawak menghalang sebarang kemungkinan gangguan dari frekuensi AC di sekitarnya.

Mod Pemilih State Output

IC juga dilengkapi dengan 'mode pemilihan keadaan output' yang berguna yang dapat digunakan untuk memungkinkan pin output berada dalam keadaan monostable atau bistable sebagai tindak balas terhadap penginderaan kapasitif dari pinout input. Ia diberikan dengan cara berikut:

Mod # 1 (TYPE diaktifkan pada Vss): Output diberikan aktif selama sp selama input ditahan di bawah pengaruh kapasitif luaran.

Mod # 2 (JENIS diaktifkan pada VDD / NTRESD): Dalam mod ini output dihidupkan dan MATI secara bergantian (tinggi dan rendah) sebagai tindak balas kepada interaksi kapasitif seterusnya di kerajang sensor.

Mode # 3 (CTYPE diaktifkan antara TYPE dan VSS): Dengan keadaan ini pin output dipicu (rendah) untuk beberapa jangka waktu yang ditentukan sebagai tindak balas kepada setiap input penginderaan kapasitif, yang durasinya sebanding dengan nilai CTYPE dan dapat bervariasi dengan kadar kapasiti 2.5ms per nF.

Nilai standard untuk CTYPE untuk mendapatkan kelewatan sekitar 10ms dalam mod # 3 boleh menjadi 4.7nF, dan nilai maksimum yang dibenarkan untuk CTYPE adalah 470nF, yang boleh mengakibatkan kelewatan sekitar satu saat. Sebarang intervensi atau pengaruh kapasitif yang tiba-tiba dalam tempoh ini tidak diendahkan.

Cara Menggunakan Litar

Pada bahagian berikut kita mempelajari konfigurasi litar khas menggunakan IC yang sama yang dapat diterapkan di semua produk yang memerlukan jarak jauh yang tepat jarak operasi dirangsang .

Sensor jarak kapasitif yang dicadangkan boleh digunakan secara beragam dalam banyak aplikasi yang berbeza seperti yang ditunjukkan dalam data berikut:

Konfigurasi aplikasi khas menggunakan IC dapat dilihat di bawah:

Konfigurasi Litar Aplikasi

Bekalan input + dilampirkan dengan VDD. Kapasitor pelicin sebaiknya disambungkan melintasi dan VDD dan ground dan juga di seluruh VDDUNTREGD dan ground untuk kerja cip yang lebih dipercayai.

Nilai kapasitansi COLIN seperti yang dihasilkan pada pin CLIN menetapkan kadar persampelan dengan berkesan. Peningkatan kadar persampelan dapat memungkinkan peningkatan masa reaksi pada input penginderaan dengan peningkatan yang berkadar dalam penggunaan semasa

Plat Sensor Kedekatan

Plat pengesan kapasitif penginderaan dapat dalam bentuk kerajang logam mini atau pelat terlindung dan diasingkan dengan lapisan tidak konduktif.

Kawasan penginderaan ini dapat ditamatkan pada jarak yang lebih jauh melalui kabel koaksial CCABLE yang hujungnya boleh dihubungkan dengan IN IC, atau plat boleh dihubungkan secara langsung dengan INpinout IC bergantung pada keperluan aplikasi.

IC dilengkapi dengan litar penapis hantaran rendah dalaman yang membantu menyekat semua bentuk gangguan RF yang mungkin cuba masuk ke IC melalui pin IN IC.

Sebagai tambahan seperti yang ditunjukkan dalam gambar, seseorang juga dapat menambahkan konfigurasi luaran menggunakan RF dan CF untuk meningkatkan penekanan RF dan memperkuat kekebalan RF untuk rangkaian.

Untuk mencapai prestasi yang optimum dari rangkaian, disarankan agar jumlah nilai kapasitansi CSENSE + CCABLE + Cp berada dalam julat yang sesuai, tahap yang baik dapat sekitar 30pF.

Ini membantu gelung kawalan berfungsi dengan cara yang lebih baik dengan kapasitansi statik berbanding CSENSE untuk menyamakan interaksi yang lebih perlahan pada plat kapasitif penginderaan.

Mencapai Input Kapasitif yang Meningkatkan

Untuk mencapai peningkatan tahap input kapasitif, mungkin disarankan untuk memasukkan perintang tambahan Rc seperti yang ditunjukkan dalam rajah yang membantu untuk mengawal waktu pelepasan sesuai dengan spesifikasi keperluan waktu dalaman.

Luas keratan rentas pelat penginderaan yang dilekatkan atau kerajang penginderaan menjadi sebanding langsung dengan kepekaan litar, bersamaan dengan nilai kapasitor Ccpc, pengurangan nilai Ccpc dapat mempengaruhi kepekaan plat penginderaan. Oleh itu untuk mencapai kepekaan yang berkesan, Ccpc dapat ditingkatkan secara optimum dan sesuai.

CPC bertanda pinout dikaitkan secara dalaman dengan impedans tinggi dan oleh itu mungkin rentan terhadap arus kebocoran.

Pastikan Ccpc dipilih dengan PPC berkualiti tinggi dari jenis kapasitor MKT atau jenis X7R untuk mendapatkan prestasi optimum dari reka bentuk.

Beroperasi pada Suhu Rendah

Sekiranya sistem dimaksudkan untuk dioperasikan dengan kapasitansi input terbatas hingga 35pF dan pada suhu beku -20 darjah C, maka disarankan untuk menurunkan voltan bekalan ke IC ke sekitar 2.8V. Ini seterusnya menurunkan julat voltan Vlicpc yang spesifikasinya antara 0.6V hingga VDD - 0.3V.

Lebih jauh lagi, menurunkan julat operasi Vucpc dapat mengakibatkan penurunan julat kapasitansi input litar secara berkadar.

Juga, seseorang mungkin memperhatikan bahawa ketika nilai Vucpc meningkat dengan penurunan suhu seperti yang ditunjukkan dalam diagram, yang memberitahu kita mengapa menurunkan voltan bekalan dengan tepat membantu penurunan suhu.

Spesifikasi Komponen yang Disyorkan

Jadual 6 dan Jadual7 menunjukkan rentang nilai komponen yang disarankan yang dapat dipilih dengan tepat sesuai spesifikasi aplikasi yang diinginkan dengan merujuk pada petunjuk di atas.

Rujukan: https://www.nxp.com/docs/en/data-sheet/PCF8883.pdf

Sebelumnya: Sinewave UPS menggunakan PIC16F72 Seterusnya: Litar Pengawal Cas Suria 3 MPPT Terbaik untuk Pengecasan Bateri Yang Efisien