Dalam domain elektronik, konsep paling penting yang digunakan oleh setiap komponen adalah ' Gerbang Logik '. Oleh kerana konsep gerbang logik dilaksanakan dalam setiap fungsi seperti di litar bersepadu, sensor, tujuan beralih, mikrokontroler dan pemproses, tujuan penyulitan dan penyahsulitan, dan lain-lain. Selain itu, terdapat banyak aplikasi Logic Gates. Terdapat banyak jenis gerbang logik seperti Adder, Subtractor, Full Penambah , Penolak Penuh, Penolak Setengah, dan banyak lagi. Oleh itu, artikel ini memberikan maklumat kolektif mengenai litar separuh pengurangan , jadual kebenaran setengah pengurang , dan konsep yang berkaitan.

Apa itu Half Subtractor?

Sebelum membincangkan pengurangan separuh, kita harus mengetahui penolakan binari. Dalam penolakan binari, proses penolakan serupa dengan penolakan aritmetik. Dalam pengurangan aritmetik, sistem nombor asas 2 digunakan sedangkan dalam penolakan binari, nombor binari digunakan untuk pengurangan. Istilah yang dihasilkan dapat dilambangkan dengan perbezaan dan meminjam.

Setengah pengurang adalah yang paling mustahak litar logik gabungan yang digunakan dalam elektronik digital . Pada asasnya, ini adalah alat elektronik atau dengan istilah lain, kita boleh mengatakannya sebagai litar logik. Litar ini digunakan untuk melakukan pengurangan dua digit binari. Dalam artikel sebelumnya, kita sudah membincangkannya konsep half adder dan full adder circuit yang menggunakan nombor binari untuk pengiraan. Begitu juga, litar penolak menggunakan nombor binari (0,1) untuk penolakan. Litar setengah pengurang boleh dibina dengan dua gerbang logik iaitu gerbang NAND dan EX-OR . Litar ini memberikan dua elemen seperti perbezaan serta mereka meminjam.

Seperti dalam pengurangan binari, digit utama adalah 1, kita dapat menghasilkan pinjaman sementara subtrahend 1 lebih unggul daripada minuend 0 dan kerana ini, pinjaman akan diperlukan. Contoh berikut memberikan penolakan binari dua bit binari.

Digit Pertama | Digit Kedua | Beza | Pinjam |

0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

Dalam pengurangan di atas, dua digit dapat ditunjukkan dengan A dan B. Kedua digit ini dapat dikurangkan dan memberikan bit yang dihasilkan sebagai perbezaan dan meminjam.

Apabila kita memerhatikan baris pertama dan kedua, perbezaan antara baris ini, maka perbezaan dan peminjaman serupa kerana subtrahend lebih rendah daripada minuend. Begitu juga, ketika kita memerhatikan baris ketiga, nilai minuend dikurangkan dari subtrahend. Jadi perbezaan dan bit pinjaman adalah 1 kerana digit subtrahend lebih tinggi daripada digit minuend.

Litar gabungan ini adalah alat penting untuk apa jua jenis litar digital untuk mengetahui kemungkinan kombinasi input dan output. Sebagai contoh, jika pengurang mempunyai dua input maka output yang dihasilkan akan menjadi empat. O / p dari setengah pengurang disebutkan dalam jadual di bawah yang akan menunjukkan bit perbezaan dan juga bit peminjam. Penjelasan jadual kebenaran litar boleh dilakukan dengan menggunakan gerbang logik seperti pintu logik EX-OR dan operasi gerbang DAN diikuti dengan pintu TIDAK.

Menyelesaikan jadual kebenaran menggunakan Peta K ditunjukkan di bawah.

setengah peta k subtraktor

The ungkapan separuh pengurang menggunakan jadual kebenaran dan K-peta dapat dihasilkan sebagai

Beza (D) = ( xy + xy ')

= x ⊕ y

Pinjam (B) = x'y

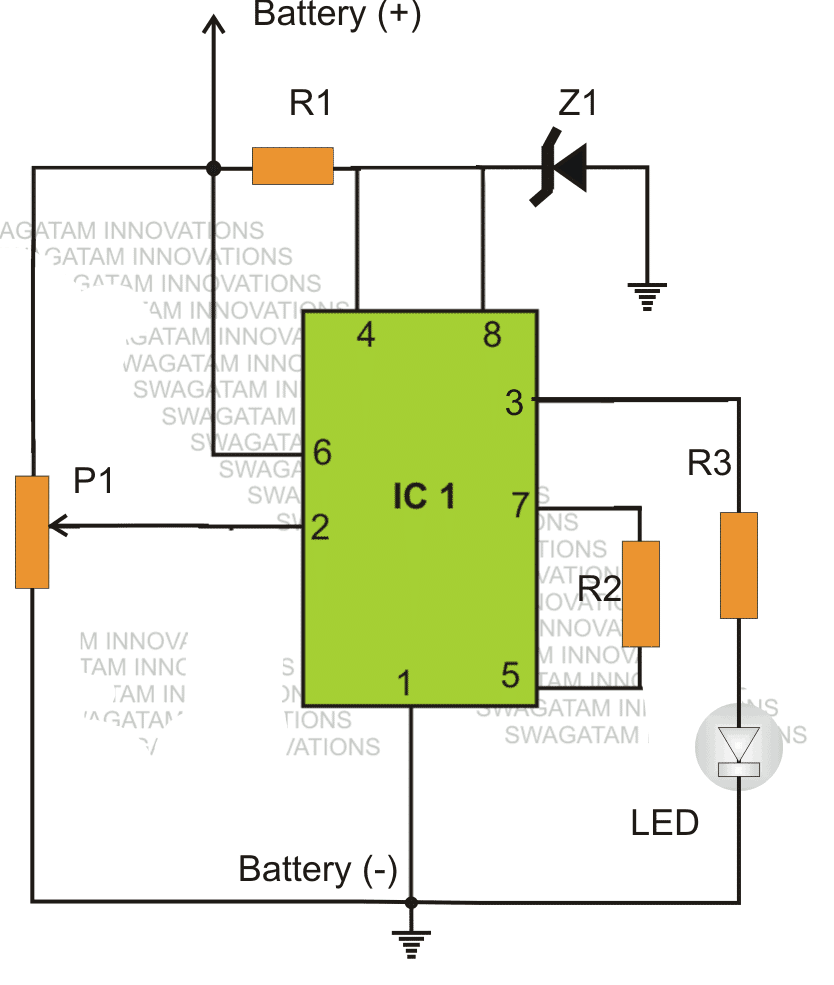

Litar Logik

The litar logik separuh pengurangan dapat dijelaskan dengan menggunakan pintu logik:

- 1 pintu XOR

- 1 BUKAN pintu

- 1 DAN gerbang

Perwakilannya adalah

Litar Logik Setengah Subtraktor

Rajah Blok Separuh Pengurangan

Gambarajah blok subtraktor setengah ditunjukkan di atas. Ia memerlukan dua input serta memberikan dua output. Di sini input ditunjukkan dengan A&B, dan outputnya adalah Difference and Borrow.

Litar di atas boleh direka dengan gerbang EX-OR & NAND. Di sini, gerbang NAND boleh dibina dengan menggunakan gerbang DAN dan BUKAN. Oleh itu, kami memerlukan tiga pintu logik untuk membuat setengah litar pengurangan iaitu pintu EX-OR, NOT gate, dan NAND gate.

Gabungan gerbang DAN dan TIDAK menghasilkan gerbang gabungan yang berbeza bernama NAND Gate. Output gerbang Ex-OR akan menjadi bit Perbezaan dan keluaran NAND Gate akan menjadi bit Pinjaman untuk input A&B yang sama.

DAN-Gerbang

Gerbang AND adalah satu jenis gerbang logik digital dengan pelbagai input dan satu output dan berdasarkan kombinasi input, ia akan melakukan penyatuan logik. Apabila semua input gerbang ini tinggi, maka output akan tinggi jika tidak, outputnya akan rendah. Gambarajah logik pintu AND dengan jadual kebenaran ditunjukkan di bawah.

DAN Gerbang Dan Jadual Kebenaran

BUKAN Pintu

Gerbang NOT adalah satu jenis gerbang logik digital dengan satu input dan berdasarkan input output akan dibalikkan. Contohnya, apabila input gerbang NOT tinggi maka outputnya akan rendah. Gambarajah logik NOT-gate dengan jadual kebenaran ditunjukkan di bawah. Dengan menggunakan pintu logik jenis ini, kita dapat melaksanakan gerbang NAND dan NOR.

BUKAN Jadual Gerbang Dan Kebenaran

Ex-OR Gate

Gerbang Exclusive-OR atau EX-OR adalah salah satu jenis gerbang logik digital dengan 2-input & output tunggal. Cara kerja pintu logik ini bergantung pada pintu OR. Sekiranya ada input dari pintu ini tinggi, maka output dari pintu EX-OR akan tinggi. Jadual simbol dan kebenaran EX-OR ditunjukkan di bawah.

Gerbang XOR Dan Jadual Kebenaran

Litar Subtractor Setengah menggunakan Nand Gate

Perancangan subtraktor dapat dilakukan dengan menggunakan pintu logik seperti pintu NAND & pintu Ex-OR. Untuk merancang litar separuh pengurang ini, kita harus mengetahui dua konsep iaitu perbezaan dan meminjam.

Litar Subtractor Setengah menggunakan Nand Gate

Sekiranya kita memantau dengan berhati-hati, cukup jelas bahawa ragam operasi yang dilakukan oleh litar ini yang secara tepat berkaitan dengan operasi gerbang EX-OR. Oleh itu, kita boleh menggunakan gerbang EX-OR untuk membuat perbezaan. Dengan cara yang sama, pinjaman yang dihasilkan oleh litar setengah penambah dapat dicapai dengan menggunakan gabungan gerbang logik seperti gerbang AND dan gerbang TIDAK.

HS ini juga boleh dirancang dengan menggunakan gerbang NOR di mana ia memerlukan 5 gerbang NOR untuk pembinaannya. Gambarajah litar setengah pengurang menggunakan gerbang NOR ditunjukkan seperti:

Setengah Pengurang Menggunakan Nor Gates

Jadual Kebenaran

Bit Pertama | Bit Kedua | Beza (EX-ATAU Keluar) | Pinjam (NAND Keluar) |

0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

VHDL dan Testbench Code

Kod VHDL untuk setengah pengurang dijelaskan seperti berikut:

perpustakaan IEEE

gunakan IEEE.STD_LOGIC_1164.ALL

gunakan IEEE.STD_LOGIC_ARITH.ALL

gunakan IEEE.STD_LOGIC_UNSIGNED.ALL

entiti Half_Sub1 adalah

Pelabuhan (a: dalam STD_LOGIC

b: dalam STD_LOGIC

HS_Diff: keluar STD_LOGIC

HS_Pinjaman: keluar STD_LOGIC)

tamat Separuh_Sub1

seni bina Kelakuan Half_Sub1 adalah

bermula

HS_Diff<=a xor b

HS_Pinjaman<=(not a) and b

The kod testbench untuk HS dijelaskan seperti di bawah:

PERPUSTAKAAN IEEE

GUNAKAN ieee.std_logic_1164.ALL

ENTITAS HS_tb ADALAH

TAMAT HS_tb

ARKITEK HS_tb DARI HS_tb IS

KOMPONEN HS

PELABUHAN (a: DALAM std_logic

b: DALAM std_logic

HS_Diff: OUT std_logic

HS_Borrow: OUT std_logic

)

KOMPONEN TAMAT

beri isyarat a: std_logic: = ‘0’

isyarat b: std_logic: = ‘0’

isyarat HS_Diff: std_logic

isyarat HS_Borrow: std_logic

BERMULA

baru: PET PORT HS (

a => a,

b => b,

HS_Diff => HS_Diff,

HS_borrow => HS_borrow

)

stim_proc: proses

bermula

ke<= ‘0’

b<= ‘0’

tunggu 30 ns

ke<= ‘0’

b<= ‘1’

tunggu 30 ns

ke<= ‘1’

b<= ‘0’

tunggu 30 ns

ke<= ‘1’

b<= ‘1’

tunggu

proses akhir

TAMAT

Penolak Penuh Menggunakan Pengurang Separuh

Subtraktor penuh adalah peranti gabungan yang mengendalikan fungsi penolakan dengan menggunakan dua bit dan minuend dan subtrahend. Litar menganggap meminjam output sebelumnya dan ia mempunyai tiga input dengan dua output. Ketiga input tersebut adalah minuend, subtrahend dan input yang diterima dari output sebelumnya iaitu meminjam dan dua output adalah perbezaan dan pinjaman.

Diagram Logik Subtraktor Penuh

Jadual kebenaran untuk penolak penuh adalah

| Input | Keluaran | |||

| X | Y | Yin | FS_Diff | FS_Pinjaman |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Dengan jadual kebenaran di atas, gambarajah litar iklan litar logik untuk pelaksanaan subtraktor penuh menggunakan separuh pengurang ditunjukkan di bawah:

Penolak Penuh Menggunakan HS

Kelebihan dan Batasan Pengurang Setengah

Kelebihan separuh pengurang adalah:

- Pelaksanaan dan pembinaan litar ini mudah dan senang

- Litar ini menggunakan kuasa minimum dalam pemprosesan isyarat digital

- fungsi pengkomputeran dapat dilakukan pada kadar kelajuan yang lebih baik

Batasan rangkaian gabungan ini adalah:

Walaupun terdapat banyak aplikasi setengah pengurang dalam banyak operasi dan fungsi, terdapat beberapa batasan dan itu adalah:

- Litar setengah pengurangan tidak akan menerima 'Pinjaman' dari output sebelumnya di mana ini adalah kelemahan penting litar ini

- Oleh kerana banyak aplikasi masa nyata beroperasi pada pengurangan sejumlah bit, setengah alat pengurang tidak mempunyai keupayaan untuk mengurangkan banyak bit

Aplikasi Half Subtractor

Aplikasi setengah pengurang merangkumi yang berikut.

- Setengah pengurang digunakan untuk mengurangkan kekuatan isyarat audio atau radio

- Ia boleh menjadi digunakan dalam penguat untuk mengurangkan herotan bunyi

- Setengah pengurang adalah digunakan dalam ALU pemproses

- Ia dapat digunakan untuk menambah dan menurunkan operator dan juga mengira alamat

- Setengah pengurang digunakan untuk mengurangkan nombor lajur yang paling tidak signifikan. Untuk pengurangan nombor berbilang digit, ia boleh digunakan untuk LSB.

Oleh itu, dari teori setengah pengurang di atas, akhirnya, kita dapat menutup bahawa dengan menggunakan litar ini kita dapat mengurangkan dari satu bit binari dari yang lain untuk memberikan output seperti Difference and Borrow. Begitu juga, kita boleh merancang separuh pengurang menggunakan litar gerbang NAND dan juga gerbang NOR. Konsep lain yang perlu diketahui adalah apa itu kod verilog separuh pengurang dan bagaimana rajah skema RTL dapat dilukis?