Kelemahan utama dari litar gabungan adalah, ia tidak menggunakan memori untuk menyimpan keadaan semasa dan sebelumnya. Oleh itu keadaan input sebelumnya tidak memberi kesan pada keadaan litar sekarang. Manakala, rangkaian berurutan mempunyai memori sehingga output dapat bervariasi berdasarkan input. Litar jenis ini menggunakan input, output, jam dan elemen memori sebelumnya. Di sini elemen memori boleh menjadi selak atau sandal. Litar Berurutan direka dengan pelbagai kaedah seperti dengan menggunakan ROM dan flip, PLA, CPLD (Perisian Logik yang Boleh Diprogramkan Kompleks) , FPGAs (Array Gerbang Programmable Lapangan) . Dalam artikel ini, kita akan membincangkan hanya bagaimana merancang litar berurutan menggunakan PLA.

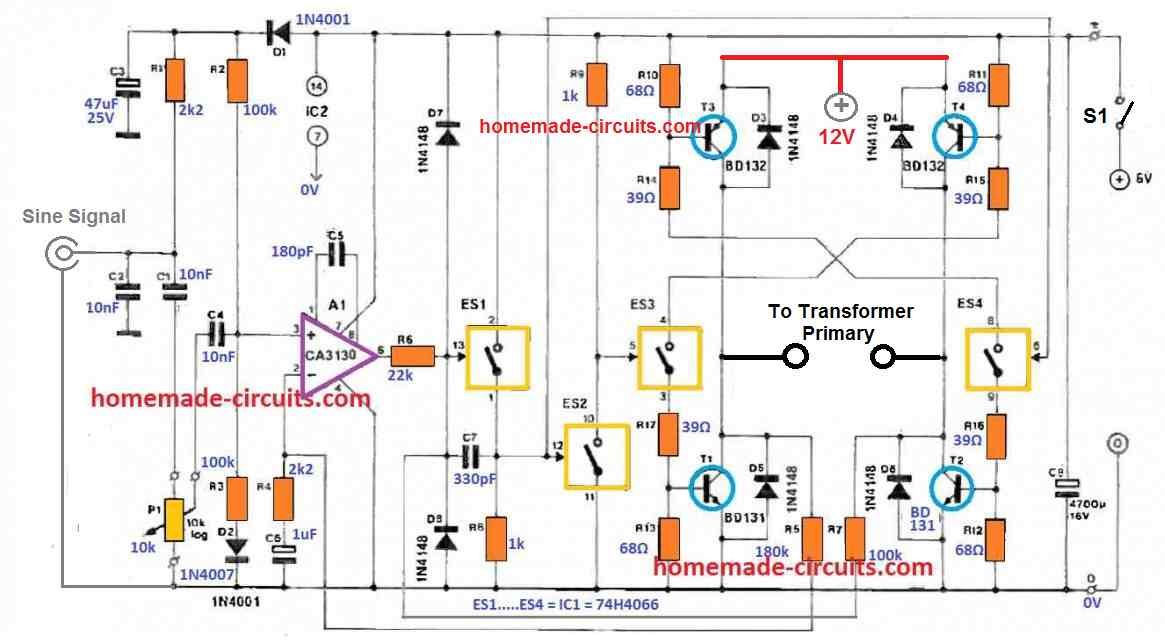

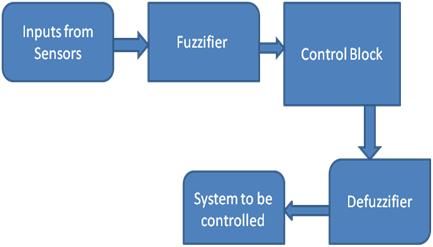

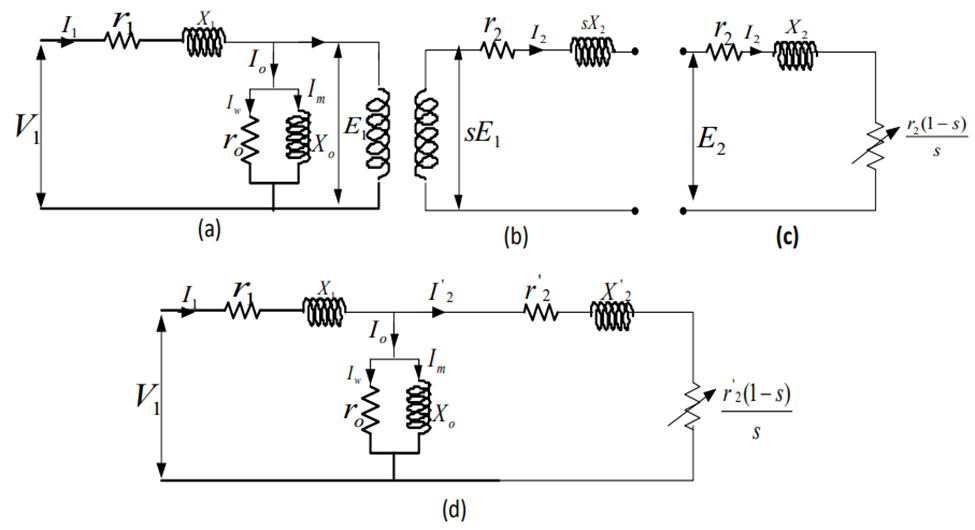

Gambarajah blok litar berurutan seperti yang ditunjukkan di bawah:

Blok Diagram Litar Berurutan

Merancang Litar Berurutan Menggunakan PLA

Litar berturutan dapat direalisasikan dengan menggunakan PLA (Aturan Logik yang Dapat Diprogramkan) dan flip-flop. Dalam reka bentuk ini, penugasan keadaan mungkin penting kerana penggunaan penugasan keadaan yang baik dapat mengurangkan jumlah syarat produk yang diperlukan dan, dengan itu, mengurangkan ukuran PLA yang diperlukan. Istilah produk yang ditakrifkan sebagai gabungan literal, di mana setiap literal adalah pemboleh ubah atau penolakannya.

Kerana mari kita mempertimbangkan reka bentuk penukar kod. Jadual keadaan yang ditunjukkan di bawah dalam jadual dapat direalisasikan dengan menggunakan satu PLA dan tiga selipar seperti rajah di bawah. Konfigurasi litar ini sangat mirip dengan reka bentuk berasaskan flip-flop ROM, kecuali bahawa ROM digantikan oleh PLA dengan ukuran yang sesuai. Tugasan negara menuju ke jadual kebenaran yang diberikan di bawah. Jadual ini dapat disimpan dalam PLA dengan empat input, 13 istilah produk, dan empat output, tetapi ini akan menawarkan ukuran yang sedikit berkurang dibandingkan dengan ROM 16 kata.

| X Q1 Q2 Q3 | Dengan D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

Jadual: Jadual Kebenaran

HADIRI NEGERI

| NEGERI SETERUSNYA X = 0 1 | HADIRI KELUAR (Z) |

| KE | B C | 1 0 |

B C | D E Dan E | 1 0 0 1 |

D ADALAH | H H H M | 0 1 1 0 |

H M | A A KE - | 0 1 1 - |

Jadual: Jadual Negeri

Merancang Litar Berurutan Menggunakan PLA

Persamaan Keluaran Input Berasal dari Peta Karnaugh

Di sini, kerana terdapat tujuh keadaan, diperlukan tiga sandal D. Oleh itu, litar PLA dengan 4 input dan 4 output diperlukan. Sekiranya penentuan keadaan penukar kod dipertimbangkan, persamaan output yang dihasilkan dan persamaan input D flip-flop yang berasal dari Karnaugh dapat ditulis persamaan berikut

D1 = Q1 + = Q2 '

D2 = Q2 + = Q2 '

D3 = Q3 + = Q1 Q2 Q3 = X 'Q1 Q3' = X Q1 'Q2'

Z = X 'Q3' + X Q3

| X Q1 Q2 Q3 | Dengan D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 sebelas

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

Jadual PLA yang sesuai dengan persamaan ini diberikan dalam jadual di atas. Jadual ini dapat direalisasikan dengan menggunakan PLA dengan empat input, tujuh istilah produk, dan empat output. Untuk mengesahkan operasi reka bentuk di atas pada mulanya, anggap bahawa X = 0 dan Q1Q2Q3 = 000. Ini memilih baris - - 0- dan 0 - - -0 dalam jadual, jadi Z = 0 dan D1D2D3 = 100. Selepas tepi jam aktif, Q1Q2Q3 = 100. Sekiranya input seterusnya adalah X = 1, maka baris - - 0 - dan - 1- - dipilih, jadi Z = 0 dan D1D2D3 = 110. Selepas tepi jam aktif, Q1Q2Q3 = 110.

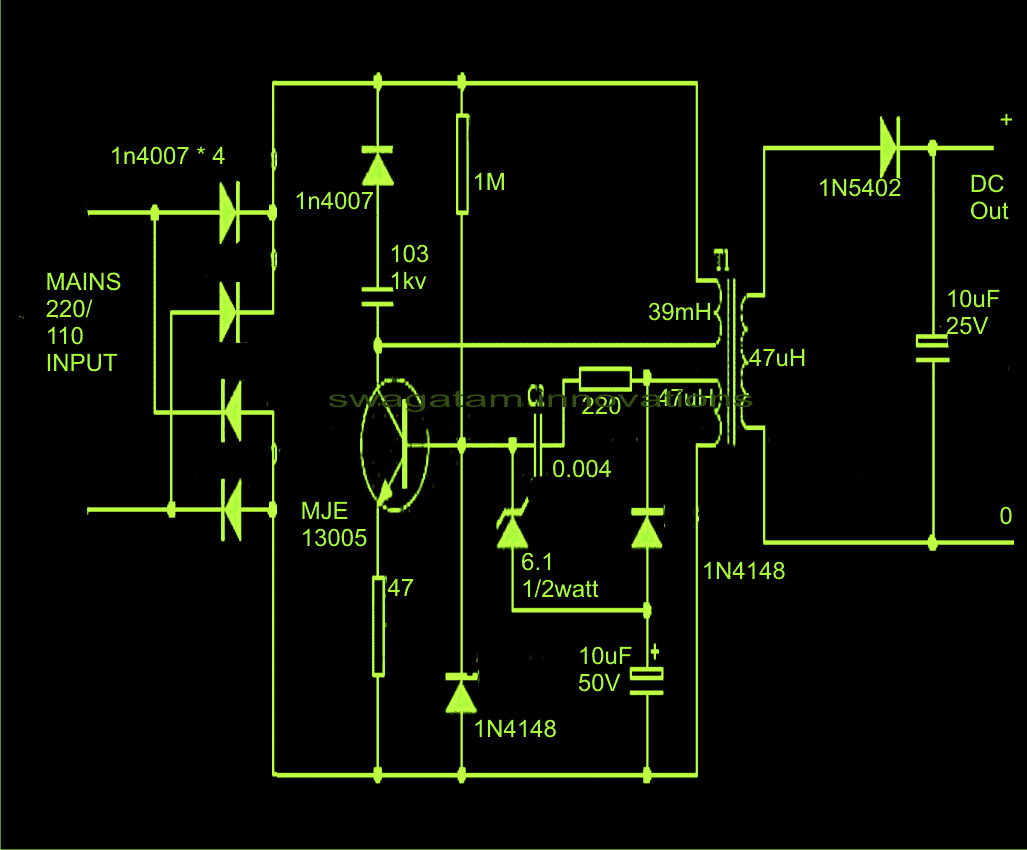

Array Logik Boleh Diprogramkan (PLA)

Logic Array yang boleh diprogramkan adalah peranti logik yang dapat diprogramkan. Ia biasanya digunakan untuk melaksanakan rangkaian logik gabungan. PLA mempunyai satu set pesawat AND yang dapat diprogram (array array), yang menghubungkan ke satu set pesawat ATAU yang dapat diprogramkan (array ATAU), yang kemudian dapat dilengkapi sementara untuk menghasilkan output. Susun atur ini memungkinkan sebilangan besar fungsi logik disintesis di jumlah produk (SOP) bentuk kanonik. Gambarajah blok ringkas PLA diberikan di bawah.

Blok Diagram PLA

Perbezaan utama antara PLA dan PAL (logik array yang dapat diprogramkan) adalah,

PLA: Kedua-duanya DAN kapal terbang dan ATAU kapal terbang boleh diprogramkan.

PAL: Hanya pesawat AND yang boleh diprogramkan, sementara pesawat ATAU tetap.

Untuk pemahaman yang lebih baik mengenai PLA, di sini kita mempertimbangkan contoh di bawah.

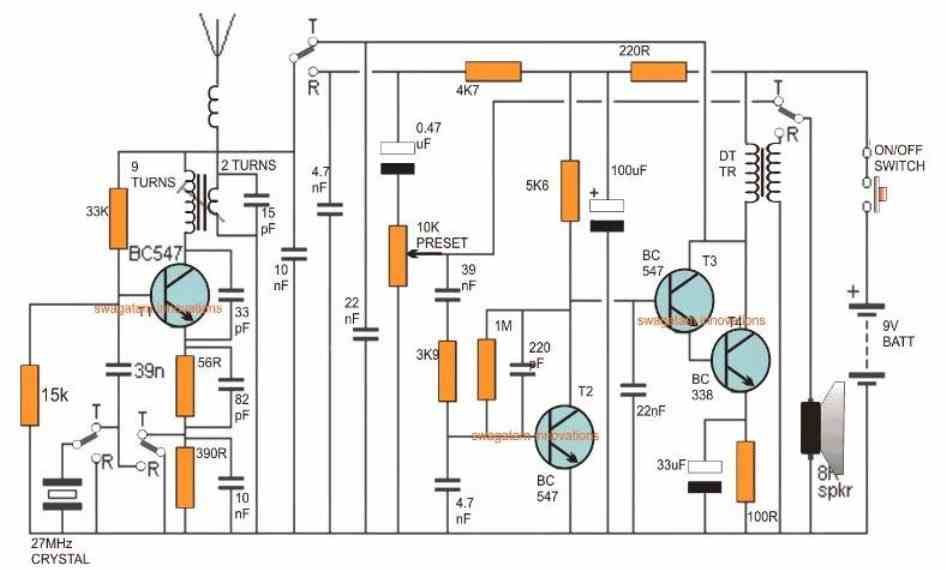

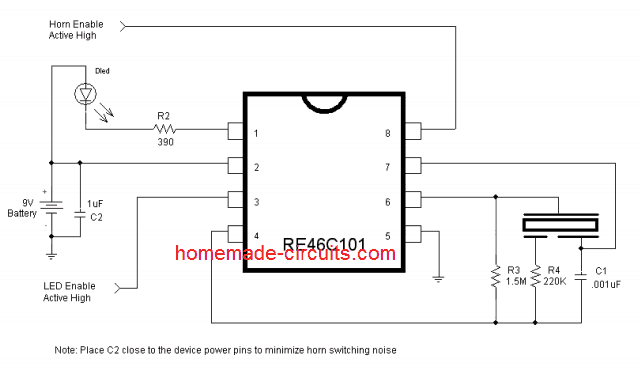

Mari cuba melaksanakan fungsi ini f1 dan f2 diberikan sebagai

Input x1, x2, x3 dan isyarat pelengkap masing-masing diberikan kepada satah DAN yang dapat diprogramkan, di sana kita akan mendapat output satah DAN sebagai minterms P1, P2, P3. Kemudian isyarat ini diberikan kepada pesawat ATAU yang dapat diprogramkan untuk menghasilkan fungsi output yang diperlukan f1 dan f2 (jumlah produk). Gambar di bawah menerangkan tahap pelaksanaan PLA untuk fungsi tertentu.

Pelaksanaan PLA

Ini semua mengenai Reka Bentuk Litar Berurutan Menggunakan PLA. Kami berpendapat bahawa maklumat yang diberikan dalam artikel ini sangat membantu anda untuk memahami konsep ini dengan lebih baik. Selanjutnya, sebarang pertanyaan mengenai artikel ini atau bantuan dalam melaksanakan projek elektrik dan elektronik , anda boleh menghampiri kami dengan memberi komen di bahagian komen di bawah. Inilah soalan untuk anda, Apakah maksud litar berurutan?